参考内容:

BUCK 电路通过控制占空比来达到降压的目的,添加 LC 二阶低通滤波器将高频部分滤除,即可达到稳定输出直流的目的。但是滤波不能完全滤除高频分量,BUCK 从原理上就决定了其纹波不容易做到很小,其固有的开关频率会导致电源噪声很大,用来给噪声敏感的元器件供电就不合适。

相比 BUCK 来说,LDO(Low Dropout Regulaor:低压差线性稳压器)输出的电压会更加平稳,可以弥补 BUCK 输出纹波大的缺点。

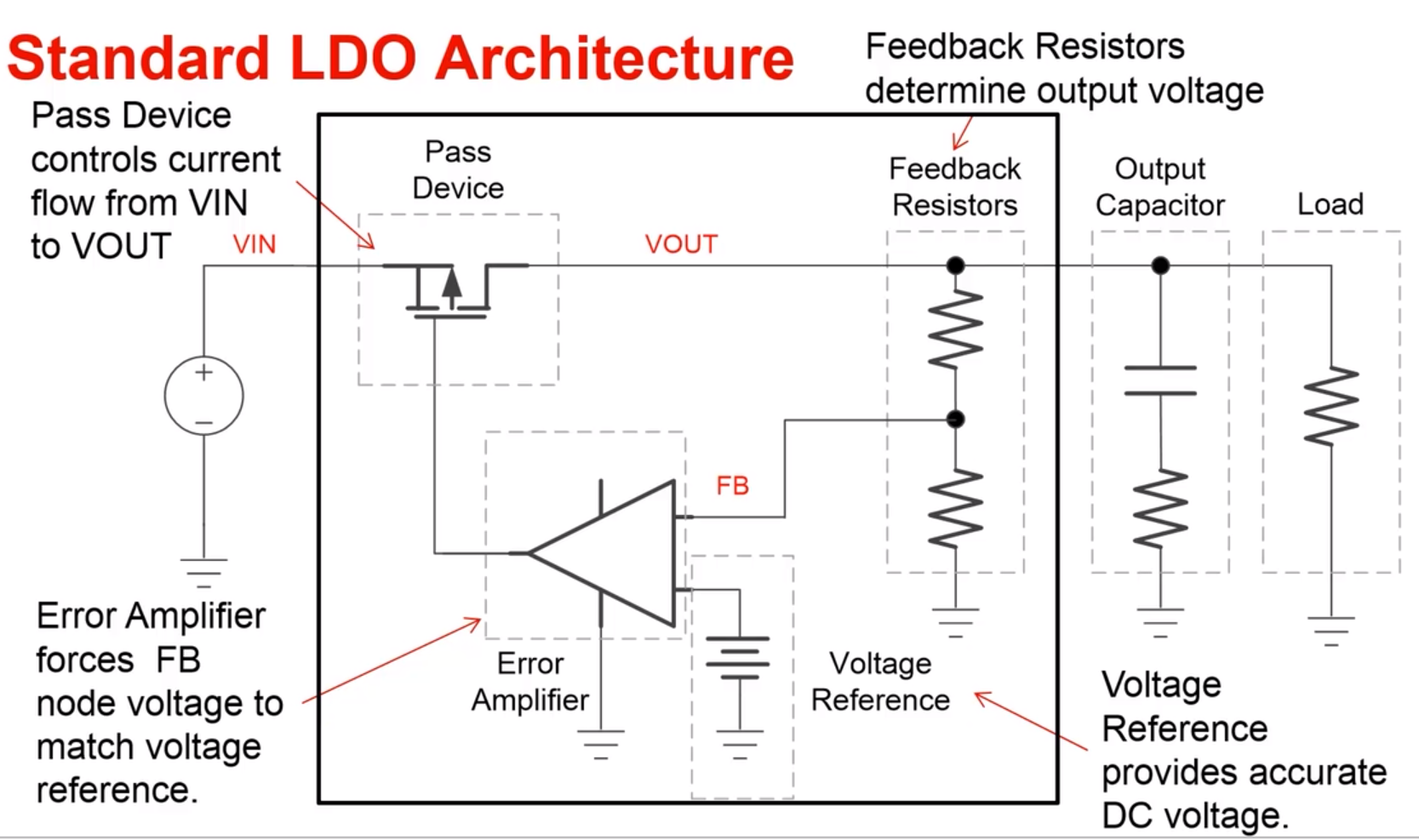

总体框图

线性稳压器主要由四部分组成,基准源用于提供精准的电压基准、导通器件用于控制从 VIN 到 VOUT 的电流大小、误差放大器将强制反馈节点与基准电压匹配、反馈电阻用于调整以改变输出电压。

从框图中也可以看到线性稳压器只能用于降压,因此输入电压必须高于输出电压。当然其名字中本身带了低压差的,低压差就意味着少的发热,意味着电源转化效率的提升。线性则是指器件的工作状态,器件的内部模块工作在放大区,放大状态呈线性关系。

工作原理

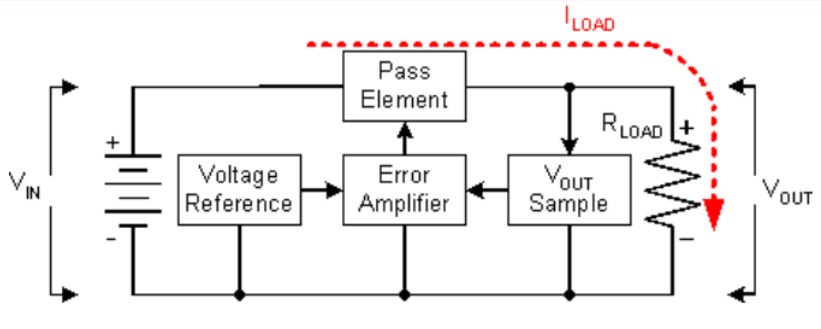

线性稳压器的工作可以模拟为两个电阻器和一个用于 VIN 的电源,其中电源用于给负载供电,通过调整可变电阻(导通器件)的阻值来控制负载电阻所获得的电压,整个系统中唯一不变的恒定的参数就是输出电压 VOUT。

其稳压过程如下图所示,当负载电压升高/降低时,采样电路所采到的电压就跟着升高/降低,传递给误差放大器后通过调节导通器件的导通程度来调节输出电压。

导通器件

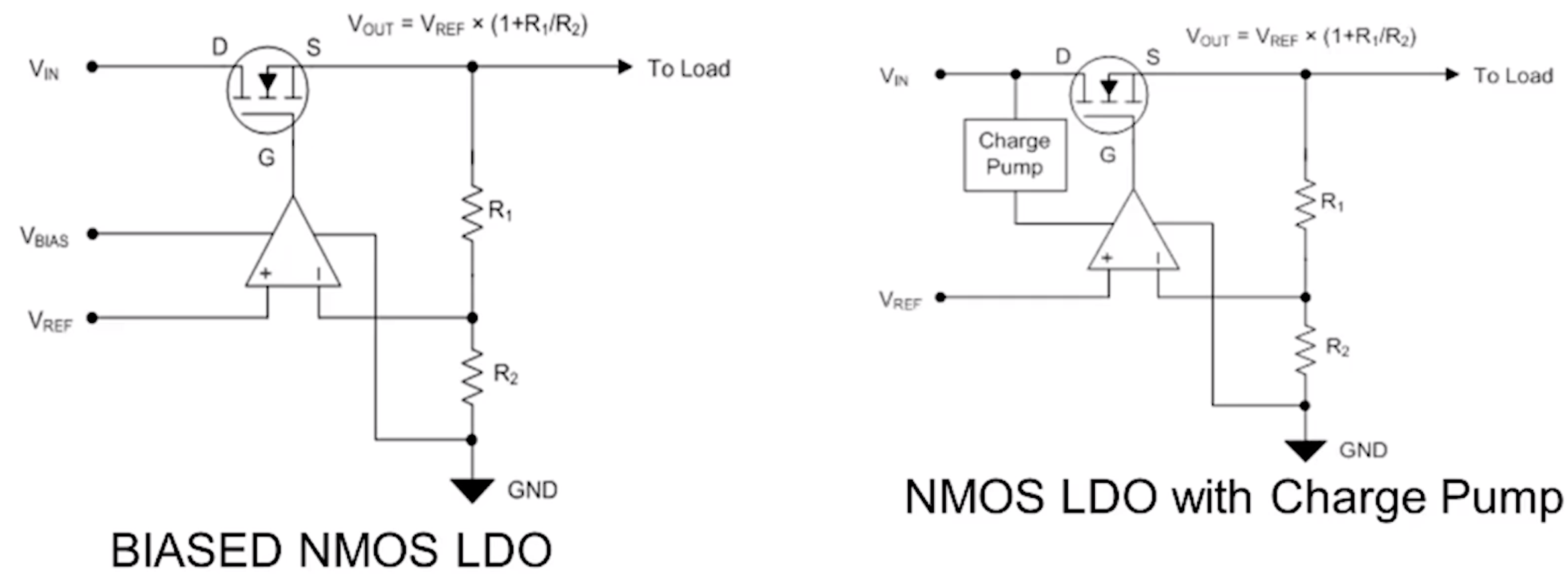

导通器件常见的有 PMOS、NMOS、BJT 等。BJT 应用于大电流的场景。PMOS 不需要额外的电源轨即可控制其导通程度,但是相比 NMOS 其 RDSon 更大,即 PMOS 架构的 LDO 在芯片本身所消耗的能量会更大。

使用 NMOS 作为导通器件时,需要添加辅助电源轨或者使用电荷泵才能将 NMOS 打开。当然电荷泵也有其缺点,虽然电荷泵可以提升 VIN,但是也带来了额外的噪声影响。若采用辅助电源轨时则需要注意,VBIAS 会影响 NMOS 的导通程度,进而影响输出电压的大小。

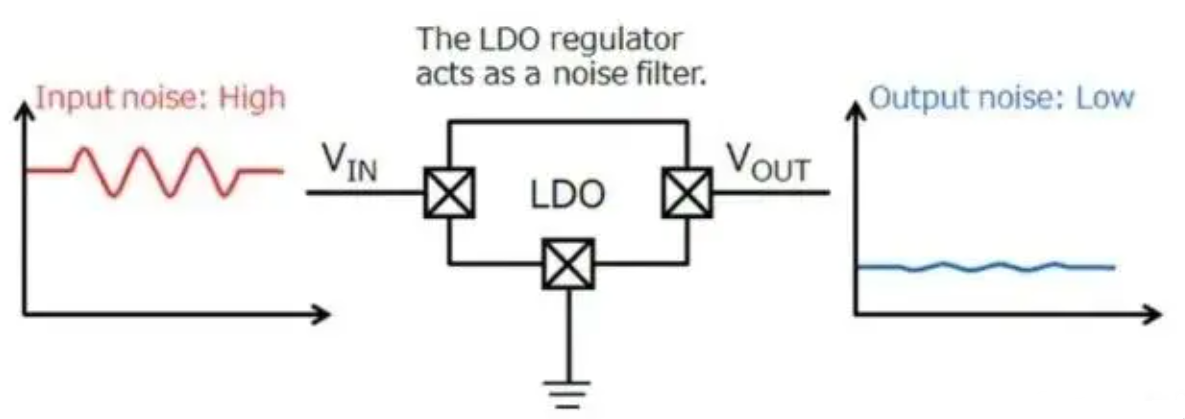

PSRR

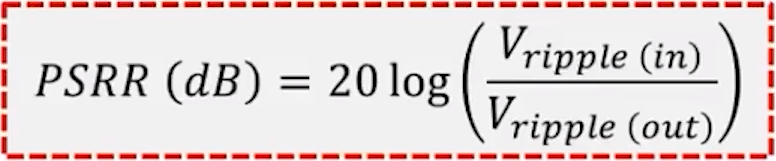

PSRR(Power Supply Rejection Ratio)量化了 LDO 抑制任何电源变化传递到其输出信号的能力,也就是 PSRR 决定了输入耦合到输出的噪声有多少。除了 LDO 本身的设计影响 PSRR 外,也可以通过调整 VIN 与 VOUT 之间的差值、输出电容来提高在特定应用(频率)下的 PSRR。

输入输出电容

为了确保 LDO 稳定工作,会在 LDO 输入输出端增加旁路电容,并且旁路电容的 ESR 需要很小,即在符合最小电容和最大 ESR 的要求下,使用任何质量良好的电容都可采用。在选择电容时还需要注意由于直流电压偏置、温度变化、制造商容差等需要对电容进行一定的降额。

输出电容除了可以进行滤波外,还会影响负载电流的变化的瞬态响应,采用较大的输出电容可以改善 LDO 对大负载电流变化的瞬态响应。输入电容则可以降低电路对 PCB 布局的敏感性,尤其是在长输入走线或者高源阻抗的情况下。

多层陶瓷电容、固态钽点解电容、铝电解电容通常用作输入和输出旁路电容。多层陶瓷电容具备 ESR 和 ESL 低、工作温度范围宽的优点,但是陶瓷电容中的介质材料具备压电性,振动或机械冲击可能会转化为电容上的交流噪声电压,在极端情况下可能会产生 mV 级的噪声。

压电性是在某些固体材料(晶体、陶瓷、骨头、DNA、蛋白质等)受到机械应力作用后,在材料中聚集电荷的现象。「压电」即由压力产生的电。

钽电容的优点是单位体积电容最高(CV 乘积),并且不太容易受到温度、偏执电压、震动效应的影响,在无法容忍压电效应的低噪声应用中,钽电容基本是唯一可行的选择。与陶瓷电容相比,钽电容的泄漏电流要比等值的陶瓷电容大很多倍,不适合超低电流应用。

铝电解电容往往体积较大、ESR 和 ESL 较高,漏电流相对较高,与钽电容一样不受压电效应影响,适合要求低噪声的应用场合,但是铝电解电容在航天应用中禁止使用。