参考内容:

为什么需要电平转换

在电路设计中,常常会遇到一个系统中存在不同的电平信号,比如 0.9V、1.8V、3.3V、5V 等,要使系统不同模块协同工作,就需要对电平信号进行转换。

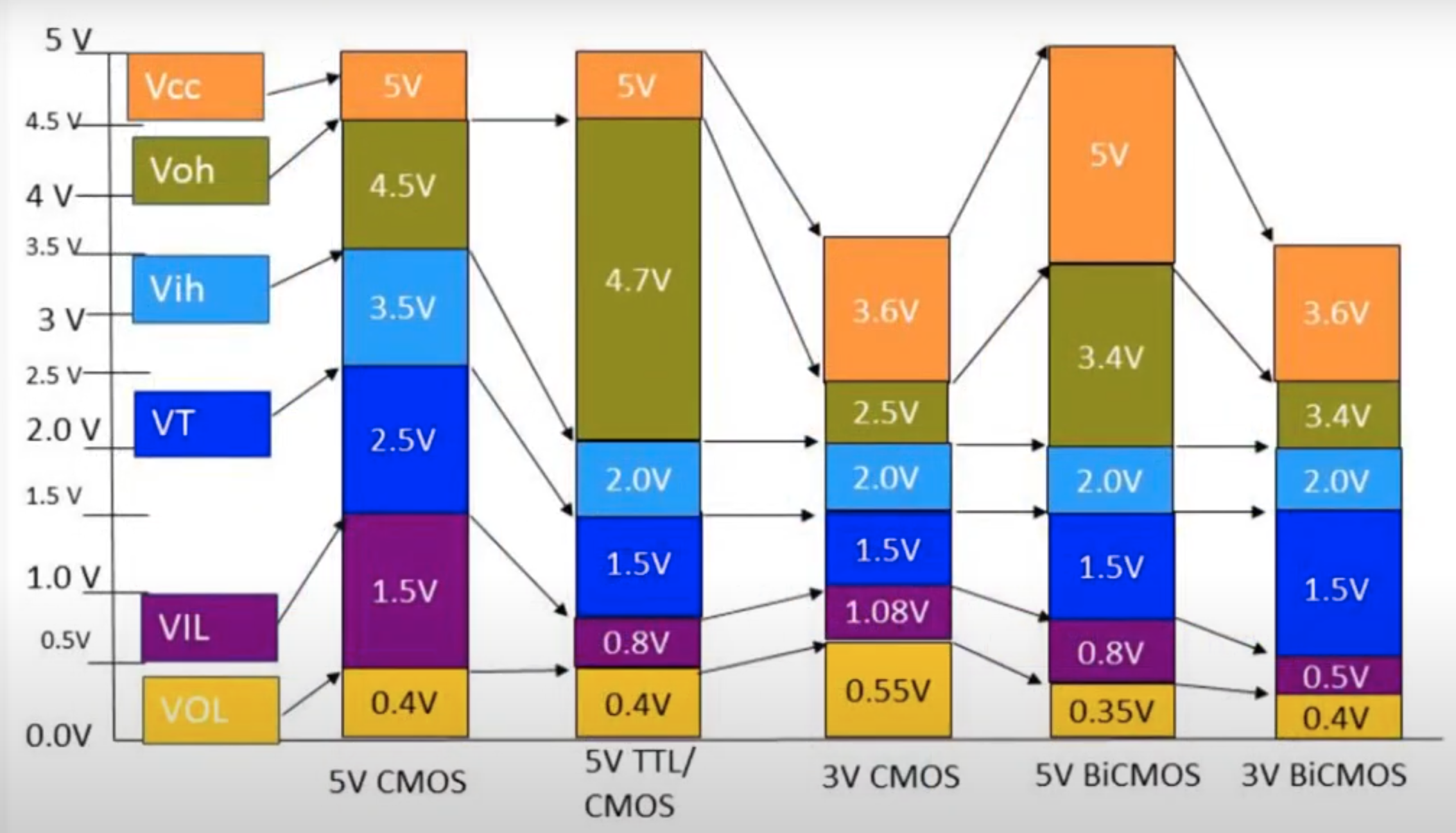

其实需要进行电平转换的本质原因是因为半导体加工工艺的不同。比如 TTL 电平 2.0V 以上表示高,0.8V 以下表示低。但是 CMOS 电平由于其物理原因,常常是将高定义为 3.5V 以上,低定义为 1.5V 以下。所以伴随着每一个新的半导体发展阶段,高和低都被改了一下,直到形成了下图这个样子。

一个 5V TTL 输出跟一个 5V TTL 输入可以没有障碍的交流,但是当一个 3V CMOS 和一个 5V CMOS 进行交流时就存在问题了。当 3V CMOS 输出高时,意味着它应用一个 2.5V 的信号在其输出引脚上,如果此时将这个输出与一个 5V CMOS 输入端进行连接,5V CMOS 只能识别超过 3.5V 的高信号和低于 1.5V 的低信号,那么 2.5V 的输入对于 5V CMOS 来说是高还是低呢?

常见电平转换电路

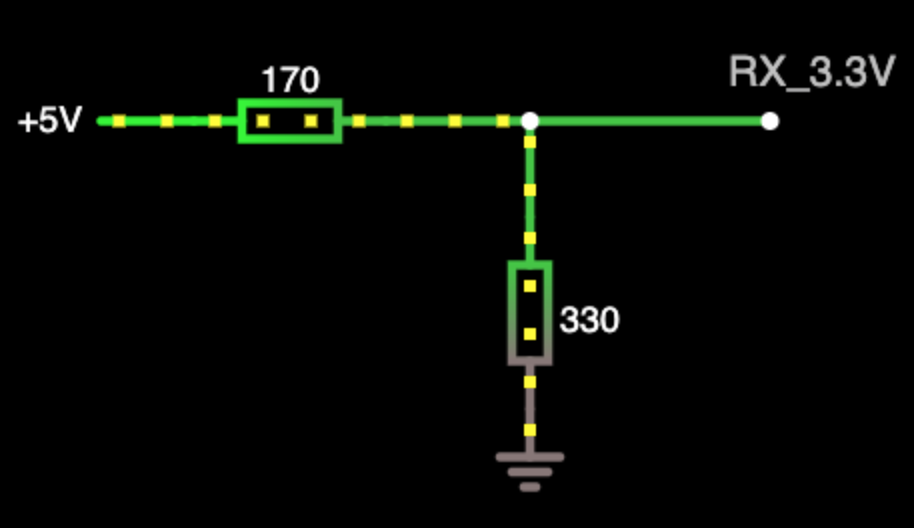

使用电阻分压

最直接也是最简单的办法就是使用电阻来分压来转换电平,后续芯片可以等效为一个负载电阻,通过串联一个电阻与芯片内部电阻构成分压关系。这种电路的优势是电阻器件采购方便、价格低廉,电路也很简单。但是缺点也很明显,因为两芯片引脚之间存在电压差且中间只有串联电阻,所以会有电流的流动造成两芯片相互影响。

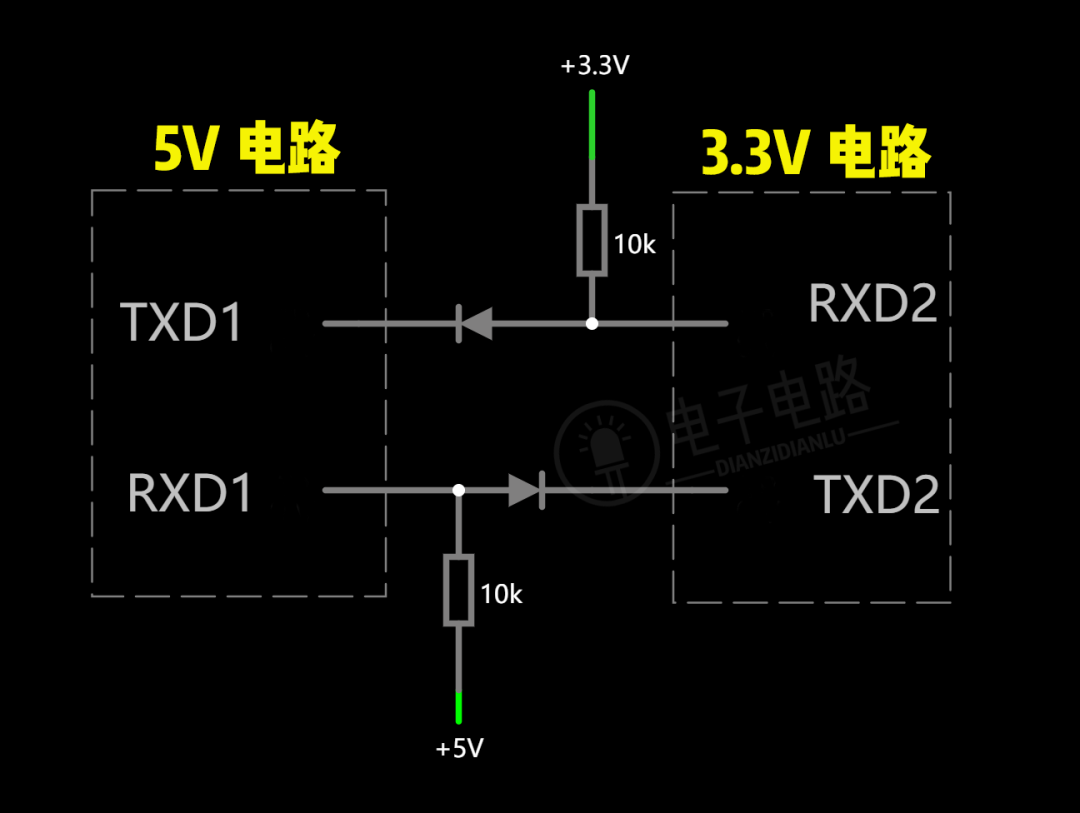

二极管电平转换

二极管电平转换电路如下图所示。该电路由二极管和电阻组成,电路使用元件比较少,其中二极管最好用肖特基二极管,因为肖特基二极管具有开关频率高和正向压降低的优点。

- 当 5V TXD1 发送高电平时,二极管正极电压比负极电压低,二极管截止,RXD2 被上拉电阻拉为高电平;

- 当 5V TXD1 发送低电平时,二极管导通,RXD2 被钳位至二极管管压降(0.7V),所以收到低电平;

- 当 3.3V TXD2 发送低电平时,二极管导通,RXD1 被钳位至二极管管压降(0.7V),所以收到低电平;

- 当 3.3V TXD2 发送高电平时,二极管也是导通的,RXD1 电压为 3.3V 加上一个管压降,即 4.0V,所以收到高电平。

当 3.3V 端发送高电平给 5V 端时,5V 端收到的并不是 5V,同时该电路只适合单向通讯的场景,发送端和接收端不可以互换。

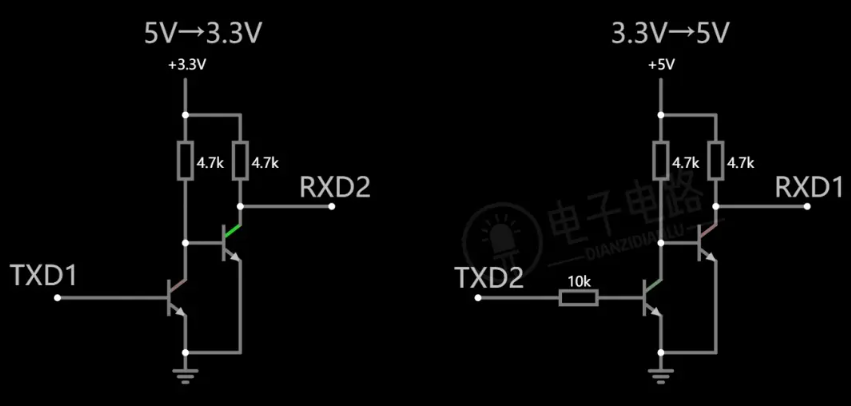

三极管电平转换

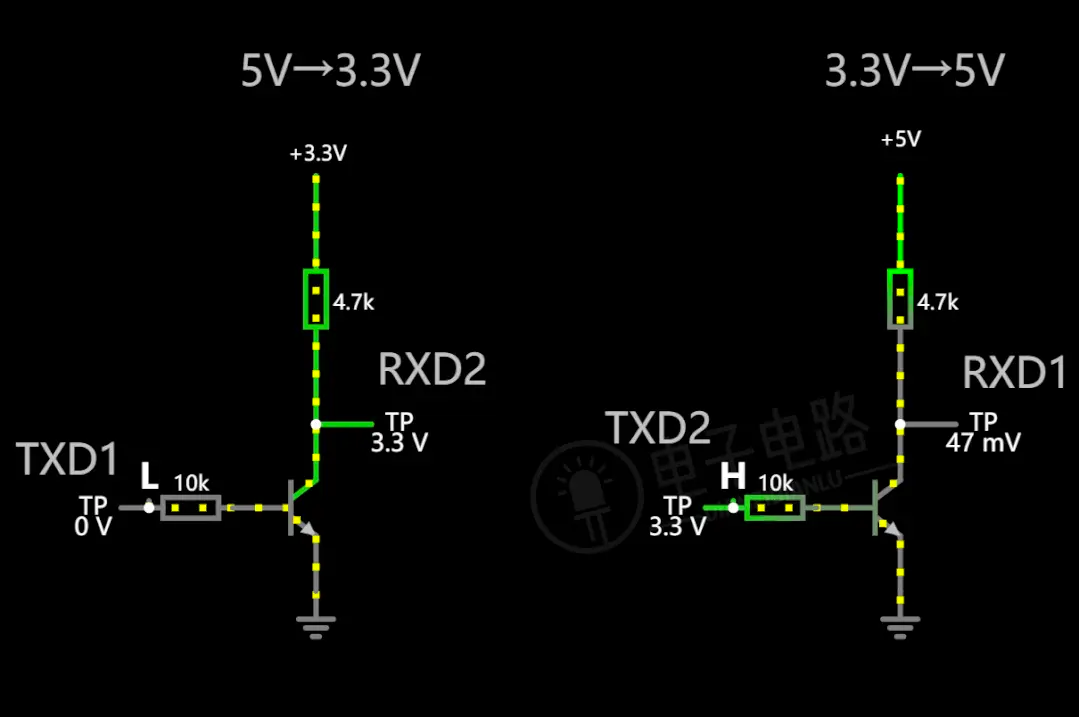

三极管电平转换电路其实就是模电中的共射极放大电路,也就是 TTL 的前身,原来的 RTL(Resistor Transistor Logic),以下图左边 5V 转 3.3V 为例。

- 当 TXD1 发送高电平时,第一个三极管导通,导致其集电极电位为低电平,所以第二个三极管基极为低电平,第二个三极管处于截止状态,RXD2 被上拉电阻拉高至 3.3V;

- 当 TXD1 发送低电平时,第一个三极管截止,第二个三极管导通,RXD2 相当于接地,输出低电平信号。

- 3V 转 5V 类似则不再赘述。

如果接收端可以接受反相信号,则可以去掉电路中一个三极管,电路会简单一些,如下图所示。

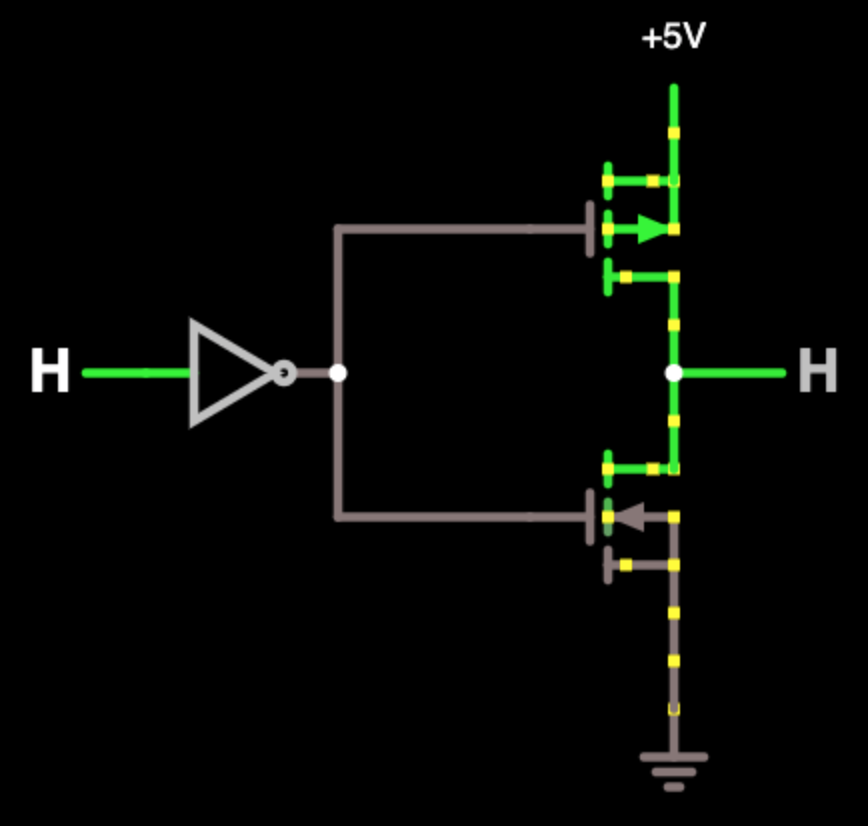

MOS 管电平转换

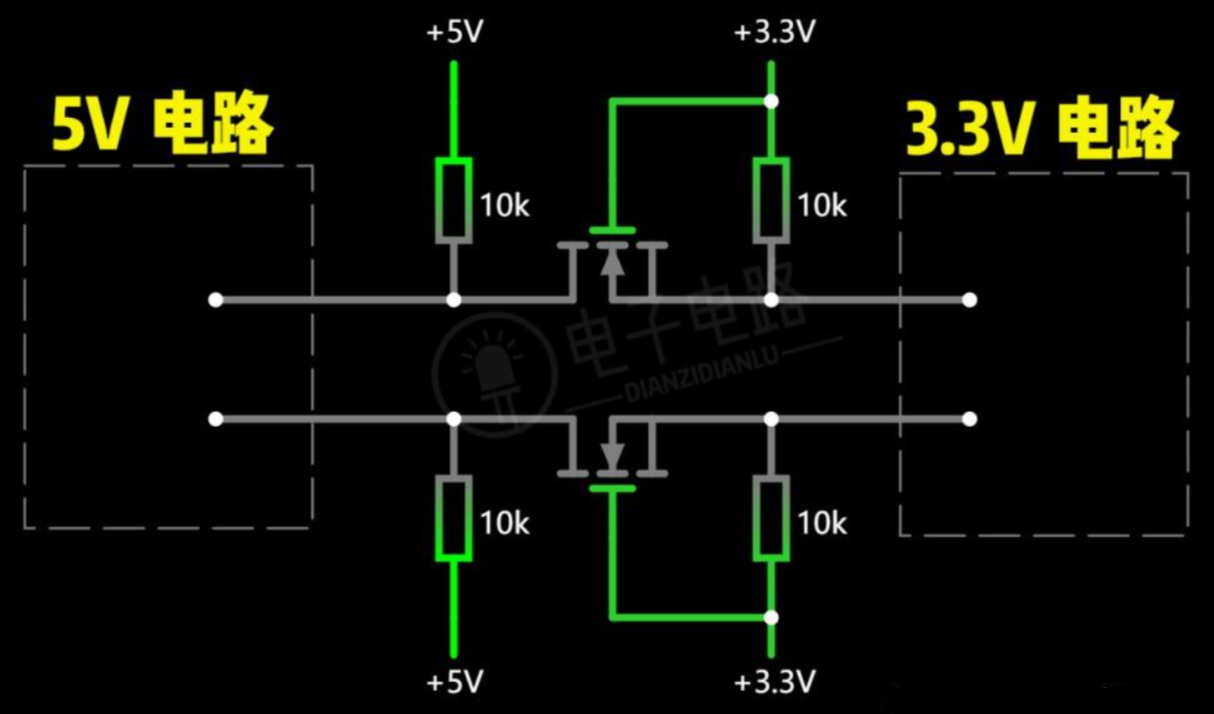

使用三极管搭建的逻辑电路的优点是速度快,但是其缺点也很明显,就是静态电流损耗很大,所以无法进行大规模的集成。MOS 管的导通电阻很小,其静态功耗可以忽略不计。MOS 管搭建的逻辑电路相比三极管的速度要慢,原因在于三极管是电流控制型器件,而 MOS 管是电压控制型器件,打开 MOS 管会涉及到给 MOS 管寄生电容充电,这个充电过程即是导致速度慢的原因。以 MOS 管搭建的如下电平转换电路可双向传输。

- 5V 电路发送高电平时,MOS 管 D 极电压被拉至 5V,但是 MOS 管的状态和 D 极电压无关,由 VGS 决定导通程度,所以 MOS 管截止,S 极被上拉电阻拉高为 3.3V;

- 5V 电路发送低电平时,MOS 管 D 极电压为 0V,S 极电压为 3.3V,由于 MOS 管存在体二极管,所以 3.3V 电路被钳位在 0.7V,为低电平;

- 3.3V 发送高电平时,MOS 管 G 极和 S 极电压都为 3.3V,MOS 管截止,D 极被上拉电阻拉高至 5V;

- 3.3V 发送低电平时,MOS 管 G 极为 3.3V,S 极为 0V,MOS 管导通,D 极为低电平。

电平转换芯片

在介绍集成好的电平转换芯片之前,我们需要先了解高阻态、三态门等基本的概念,最后再将三态门等进行组合形成电平转换芯片。

高阻态

高阻态是数字电路中常见的术语,表示电路中的某个节点具有相对电路中其它点更高的阻抗,它是电路的一种特殊的输出状态,但是这个状态既不是高电平也不是低电平。如果用万用表进行测试,可能测到高电平也可能测到低电平,它的状态取决于其后面的电路。

在电路分析时可以将高阻态作开路理解,理论上高阻态是不悬空的,它对地和对电源的电阻都非常大,但实际应用时与引脚悬空几乎一致,因此高阻态的极限可以认为就是悬空。

那么高阻态又是如何造成的呢?通常是由于三态门或三态缓冲器的存在而导致的,当三态门的使能端为低电平时,门电路输出上拉管和下拉管都截止,输出端就处于浮空状态,即没有电流的流动。此时相当于门电路放弃了对输出端电路的控制,其实际电平就由外部电平来决定。

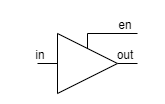

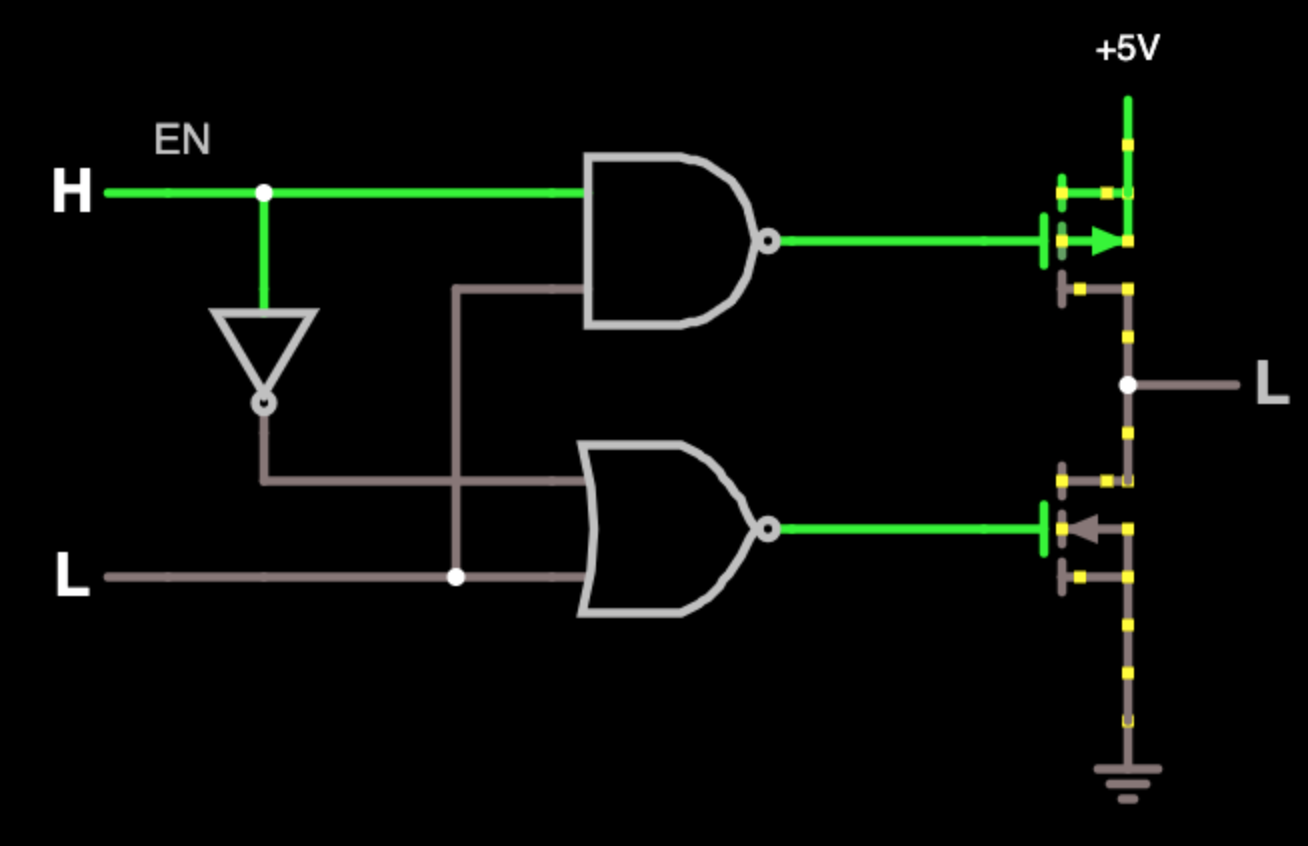

三态门

那么什么又是三态门呢?三态门允许输出端除了高电平和低电平之外呈现高阻态。可以理解为除了输出输出端口外,三态门另外加了一个 EN 引脚,若没有对三态门进行使能,则其输出为高阻态,否则输出由输入决定。

三态门常常用于总线连接结构。在总线上有多个设备连接到同一条数据线上,但是在特定时间内只有一个设备是有效的,不活动的设备处于高阻态,因此不会对总线上其它设备产生影响。一般来说需要双向数据传输,我们再增加一个三态门即可实现此功能。

三态门输出结构

三态门输出端由上 PMOS 管、下 NMOS 管和一个输出供电电压构成,当上管导通时输出低电平,当下管导通时输出为高电平。

但是仔细观察会发现输出和输入是反相的,因此为了保证输入与输出同相,我们还需要在输入端加一级反相器。神奇的事情发生了,这不是施密特触发器吗?而且实际应用时为加强电路的抗干扰能力,使用的就是施密特触发器。

我们在上文的基础上再加入 EN 使能逻辑,即可实现完整的三态门输出结构,在排故障时可通过该等效电路对现象进行分析。

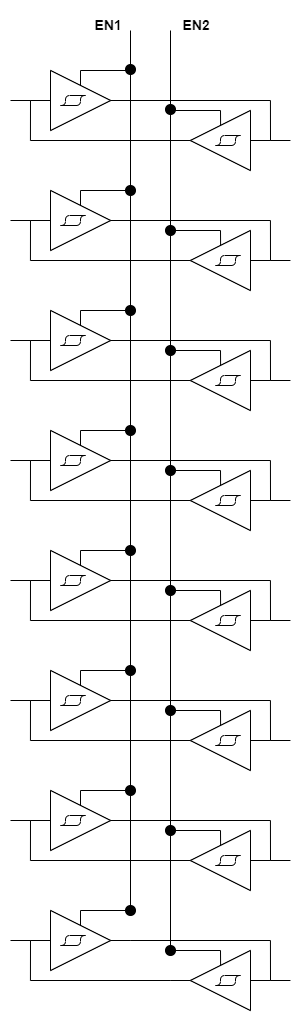

集成芯片

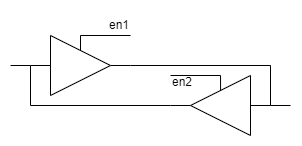

在实际应用中肯定不能一位一位的传输,我们假设一次传输一个字节(8 bit),为了简化电路我们把同一个方向的 EN 信号接到一起,如此即只需要两个信号即可控制数据的传输方向了。

通过控制 EN1 和 EN2 的使能与否,即可控制数据的传输方向。需要注意的是应该避免 EN1 和 EN2 同时都使能的状态,因为在此种状态下左右两侧的数据传输会打架,谁也不知道接收到的信号到底是自己发出去的还是别人发过来的。

| EN1 | EN2 | 左侧 | 右侧 | 输出状态 |

|---|---|---|---|---|

| H | H | 使能 | 使能 | 无效状态 |

| H | L | 使能 | 高阻态 | 数据由左至右 |

| L | H | 高阻态 | 使能 | 数据由右至左 |

| L | L | 高阻态 | 高阻态 | 隔离,不传输数据 |

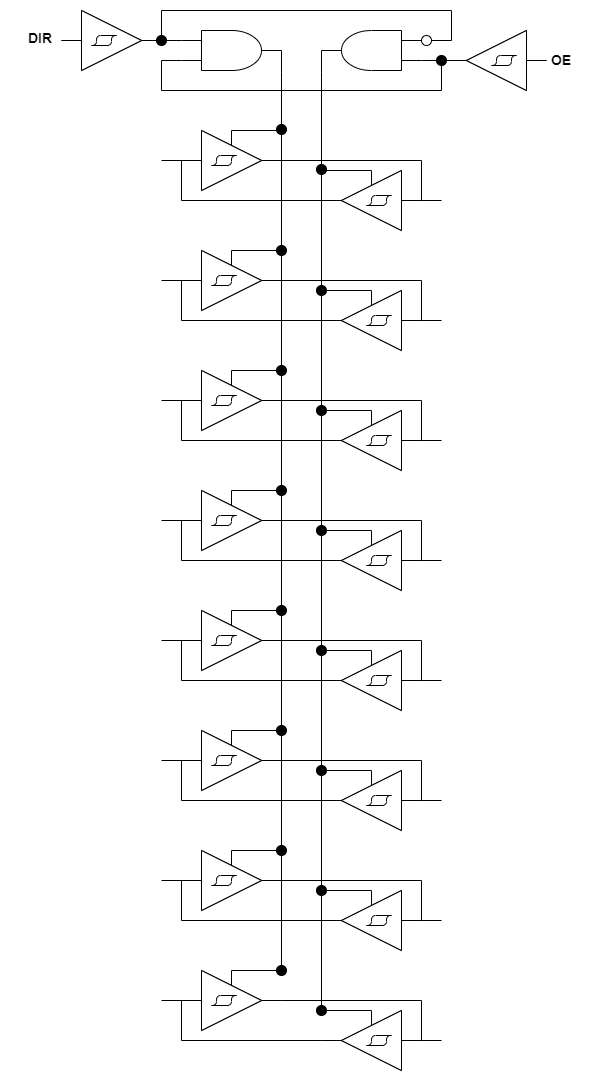

为了避免上述同时使能的状态,我们对电路做一点改进,以保证芯片不会出现稀奇古怪的现象。

| OE | DIR | 左侧 | 右侧 | 输出状态 |

|---|---|---|---|---|

| H | H | 使能 | 高阻态 | 数据由左至右 |

| H | L | 高阻态 | 使能 | 数据由右至左 |

| L | H | 高阻态 | 高阻态 | 隔离,不传输数据 |

| L | L | 高阻态 | 高阻态 | 隔离,不传输数据 |